Tervezési segédlet a Z80 (MK3880) típusú mikroprocesszor alkalmazásához

II. rész: A Z80-PIO Áramkör (MK3881 párhuzamos I/O vezérlő) |

III. rész: A Z80-CTC Áramkör (MK3882 számláló időzítő áramkör) |

|

Tartalom |

||

| 1. Bevezetés 2. A PIO felépítése 3. A kivezetések elnevezései és funkciói 4. A PIO programozása 5. Időzítés 6. Megszakítás kiszolgálás 7. Felhasználás 8. Programozási összefoglaló 9. Elektromos specifikáció 10. Rendelési információk |

11. Bevezetés 12. A CTC felépítése 13. A CTC lábkioszása 14. A CTC üzemmódjai 15. A CTC programozása 16. A CTC időzítése 17. CTC megszakítás kiszolgálás 18. Elektromos specifikáció |

|

A Z80-PIO Áramkör

A Z80 párhuzamos I/O áramköre a PIO, egy programozható, kétcsatornás TTL kompatibilis interface áramkör, amely biztosítja a Z80 processzor és a periféria áramkörök összekapcsolását. A Z80 PIO-val kialakított rendszerhez a perifériák széles skálája csatlakoztatható anélkül, hogy ehhez további áramköröket kellene felhasználni. A Z80 PIO teljesen kompatibilis perifériái közé tartozik a legtöbb tasztatura, lyukszalag olvasó, nyomtató és PROM programozó perifériák. A PIO 40 lábas tokozással és N csatornás, szilícium vezérlőelektródás technológiával készült áramkör. Főbb tulajdonságai a következők:

Az egyik egyedülálló tulajdonsága a Z80-PIO áramkörnek - ami megkülönbözteti a többi interface áramkörtől - az, hogy az adatforgalom a periféria és a CPU között tisztán megszakításokkal zajlik le. Az I/O műveleteknél a PIO logikája lehetővé teszi a Z80-CPU hatásos megszakítási lehetőségének teljes kihasználását. A teljesen egymásba ágyazott megszakítási rendszer kialakításához szükséges összes áramkör megtalálható a PIO áramkörben.

Egy másik egyedülálló tulajdonsága a PIO-nak, hogy egy meghatározott periféria státusz függvényében programozható megszakítást tud kérni a CPU-tól. Például a PIO beprogramozható úgy, hogy megszakítást kérjen, ha bármelyik vonalán hibajelzés érkezik a perifériától. Ez a megoldás szükségtelenné teszi, hogy a CPU tekintélyes időveszteséggel sorra lekérdezze a perifériák státuszát.

A Z80-PIO blokkvázlata a 2.0-1-es ábrán látható és a következő egységeket tartalmazza:

A CPU busz interface áramkör lehetővé teszi, hogy a PIO közvetlenül (további külső áramkör felhasználása nélkül) csatlakoztatható legyen a Z80-CPU buszára. Nagy rendszereknél természetesen további vonalmeghajtók és címdekóderek szükségesek. A belső vezérlő áramkör a CPU busz és a periféria áramkör csatlakozását vezérli. A két I/O csatorna (A és B) azonos és közvetlenül a perifériához csatlakozik.

A 6-6 regiszterből és a "handshake" vezérlő áramkörrel felépített I/O csatorna blokkvázlata a 2.0-2-es ábrán látható. Az egyes regiszterek a következő funkciókat látják el:

A két bites üzemmód regisztert a CPU tölti fel, amellyel beállítja a szükséges üzemmódot (8 bites ki-, vagy bemenet, kétirányú busz és bit vezérlő). A CPU és a periféria között minden adatátvitel a be- és a kimeneti regisztereken keresztül történik. A CPU bármely időben beolvashatja a bemeneti, vagy a kimeneti regiszterek tartalmát. A csatornák "handshake" kimeneti vonalai vezérlik az adatátvitelt a periféria és a PIO között. A 8 bites maszk és a 8 bites be- és kimenet választó regiszterek csak a bit vezérlő üzemmódban működnek. Ebben az üzemmódban a periféria adat, illetve vezérlő buszának bármelyik bitje programozható be- vagy kimenetnek attól függően, hogy a választó regiszter megfelelő bitjei 1-et, vagy 0-t tartalmaznak. A maszk regiszter ebben az üzemmódban egy speciális (feltételes) megszakítással kapcsolatban lát el feladatot, ami abból áll, hogy megszakítást lehet kérni attól függően, hogy néhány, vagy az összes nem maszkolt kimeneten egy meghatározott állapot (1 vagy 0) áll be. A kétbites maszk vezérlő határozza meg, hogy az összes nem maszkolt vonal aktív (ÉS kapcsolat), vagy bármely nem maszkolt vonal aktív (VAGY kapcsolat) állapotánál lesz megszakítás kérés. A PIO-nak ez a tulajdonsága feleslegessé teszi, hogy a CPU megvizsgálja a perifériák státuszát, mivel a meghatározott periféria státusznál a PIO automatikusan megszakítást kér. Például, ha egy rendszerben három hibajelző bit van, megoldható, hogy akkor generáljon megszakítást, ha valamelyik a három közül, vagy ha mind a három bit jelez.

A megszakítási logika a láncolt prioritásos rendszernek megfelelően kezeli a CPU megszakítási jeleit. Az egyes egységek prioritását a láncban elfoglalt fizikai helyük határozza meg. Két vezeték szolgál az összekapcsolásra, és a láncba kapcsolt perifériák közül a CPU-hoz közelebb állónak van nagyobb prioritása. A PIO-n belül az A csatornának van nagyobb prioritása a B csatornához viszonyítva. Bemenet, kimenet vagy kétirányú busz üzemmádban megszakítás akkor generálható, amikor a periféria új adatátvitelt kezdeményez. Bit vezérlő üzemmódban akkor lesz megszakítás kérés, ha a periféria státusza megegyezik a beprogramozott értékkel.

A PIO ellátja az egymásba ágyazott megszakítások teljes vezérlését, ami biztosítja, hogy a kisebb prioritású egység nem tud megszakítani addig, amíg a nagyobb prioritású egység rutinját be nem fejezete a CPU. A nagyobb prioritású egység megszakíthatja a kisebb prioritású egység kiszolgáló rutinját.

Amikor a CPU megszakítást fogad el (2. üzemmódban) a megszakító perifériának egy 8 bites megszakítási vektort kell kiadnia. Ez a vektor meghatározza megszakítási rutin kezdőcímét a memóriában. A periféria 8 bites vektora egy pointer alsó byte-ját határozza meg, még a felsőt a CPU I regisztere adja. A pointer egy táblázatból (a memóriában) kijelöli azt a helyet, ahol a megszakítási rutin kezdőcinre található.

Minden csatornának külön megszakítási címe van.

A megszakítási vektor legkisebb helyiértékére a PIO mindig 0-át ír, így a pointer által kijelölt két byte közül az elsőnek a címre mindig páros lesz. A PIO közvetlenül a CPU adatbuszáról dekódolja a RETI (Return from Interrupt) utasítást, ami biztosítja, hogy a rendszerben az összes PIO mindig tudja mikor folyik megszakítás kiszolgálás, anélkül, hogy ehhez a CPU-val külön üzenetváltásra lenne szükség.

3. A kivezetések elnevezései és funkciói

A Z80-PIO kivezetéseinek elrendezését és elnevezését a 3.0-1 ábra mutatja. A továbbiakban az egyes kivezetések (pinek) funkcióit írjuk le.

3.0-1 ábra: A PIO lábkiosztása

| D7-D0 | Z80-CPU adat busz (kétirányú 3 állapotú) Ezen a buszon keresztül zajlik le minden adat és utasítás forgalom a CPU és a PIO között. |

| B/A SEL | A vagy B csatorna választó bemenet |

| C/D SEL | Vezérlés vagy adat-választó bemenet (Control / Data) Ez a bemenet határozza meg az adatátvitel típusát a CPU és a PIO között. Ha logikai 1 szint van a bemeneten, mialatt a CPU adatot visz ki a PIO-ra, a PIO ezt utasításként értékeli a kiválasztott B vagy A csatorna részére. Ha logikai 0 szint van ezen a bemeneten, akkor a CPU buszán adatátvitel történik a PIO felé. Általában a CPU címbuszának A1 helyértékű bitjét használják erre a funkcióra. |

| CE | Chip engedélyező bemenet (Chip enable) Logikai 0 szint a bemeneten engedélyezi, hogy a PIO adatot vagy utasítást fogadjon el, amikor a CPU író ciklust hajt végre, vagy adatot adjon ki a CPU részére, amikor az beolvasó ciklust hajt végre. |

|

Rendszer óra (clock) bemenet. A Z80 PIO a Z80 rendszer egyfázisú óráját használja a belső műveleteinek végrehajtásához. |

| M1 | Gépi ciklus bemenet (CPU-tól jön).

|

| IORQ | I/O kérés bemenet (Input/Output Request) a CPU vezérli. |

| RD | Olvasó ciklust jelző bemenet a CPU-tól (Read). Amikor ez a bemenet logikai 0-ba van a CPU memóriából vagy az I/O egységből olvas. Az RD jel a B/A, a C/D, a CE és az IORQ jelekkel együtt az adatátvitelt vezérli a PIO és a CPU között. |

| IEI | Megszakítás engedélyező bemenet (Interrupt Enable Input). Az IEI bemenet a prioritásos megszakítási lánc kialakításához szükséges, amikor több mint egy megszakító egység van. Logikai 1 szint ezen a bemeneten jelzi, hogy nincs más nagyobb prioritású egység kiszolgálás alatt. |

| IEO | Megszakítás engedélyező kimenet (Interrupt Enable Output). Ez a másik kivezetés, ami a megszakítási lánc kialakításához szükséges. Ez csak akkor van 1 állapotban, ha az IEI bemenet 1 és a CPU nem szolgálja ki ezt az egységet. Így ez a jel tiltja le a kisebb prioritású egységeket, ha a CPU egy nagyobb prioritású egységet éppen kiszolgál. |

| INT | Megszakítás kérő kimenet (Interrupt Request). Amikor ez a jel 0 szintbe megy a Z80-PIO megszakítást kér a CPU-tól. |

| A0-A7 | Az A csatorna kimeneti busza (kétirányú, háromállapotú). Ez a busz szolgál az adatok vagy státusz, illetve vezérlések továbbítására a PIO-tól a perifériára és vissza. A0 a busz legkisebb helyértékű vonala. |

| A STB | Az A csatorna beíró bemenete (Strobe) a periféria felől (0 szint az aktív). A jel funkciója a kijelölt üzemmódtól függ:

|

| A RDY | Az A csatorna "kész" jele (Ready) kimenet, aktív állapota 1. A jel funkciója a kijelölt üzemmódtól függ:

|

| B0-B7 | B csatorna kimeneti busza (kétirányú, háromállapotú). Ez a busz szolgál az adatok, státusz és vezérlések átvitelére a PIO B csatornája és a periféria között. Ez az adatbusz 1.5 V-nál 1,5 mA-el Darlington kapcsolású tranzisztorok meghajtására is alkalmas. B0 a busz legkisebb helyiértékű vonala. |

| B STB | B csatorna beíró bemenete (Strobe) a periféria részére (aktív szintje 0). |

| B RDY | B regiszter "kész" kimenete (Ready), aktív állapota 1. A jel funkciója az alábbi kivétellel megegyezik az A RDY jel funkciójával: Az A csatorna kétirányú üzemmódjánál jelzi a perifériának, hogy az A csatorna bemeneti regisztere üres és adatot vár. |

4.1 Törlés (RESET)

A tápfeszültség megjelenésekor a Z80-PIO automatikusan reset állapotba kerül. A reset állapotban a következő műveletek végrehajtása történik:

A bekapcsolási automatikus törlésen kívül a PIO törölhető az M1 bemenettel is, ha az RD és IORQ bemenetek nem aktívak. Ebben az esetben a PIO reset állapotba megy, miután az M1-es bemenet inaktívvá vált. Így a PIO egy egyszerű külső kapu segítségével törölhető anélkül, hogy a tápfeszültséget ki kellene kapcsolni. Ez a megoldás a 40 lábas kivezetés korlátozás miatt volt szükséges. Ez a törlési mód akkor ajánlott, amikor önálló rendszerben nyomógombbal alapállapotba állítjuk az egyes egységeket.

A PIO software úton is törölhető, de ez a rendszer fejlesztés elején a hardware esetleges hibái miatt nem ajánlott. Ha a PIO reset állapotba került, ott addig marad, amíg vezérlő adatot nem kap a CPU-tól.

4.2 A megszakítási vektor betöltése

A PIO-t úgy tervezték, hogy a Z80-nal a 2. üzemmódú megszakítással kommunikáljon. Ez az üzemmód a megszakító egységtől kéri be a megszakítási címet. Ebből a címből ill. vektorból állítja elő a CPU a megszakítási rutin tényleges címét. A megszakítási vektort (a megszakítást elfogadó ciklus alatt) az a periféria helyezi a CPU adatbuszára, amelyik a legnagyobb prioritással rendelkezik a megszakítást kérő perifériák közül. (Lásd a Z80 CPU leírásának megszakítás kiszolgáló részét.) A szükséges megszakítási vektor a következő formátumban, vezérlő utasítással irható be a PI0-ba:

Ebben az esetben a D0-ás bit logikai 0 állapota jelzi, hogy az adatot a vektor regiszterbe kell tölteni. Az interrupt elfogadásakor az megszakítási vektor ugyanilyen formában kerül a Z80 adatbuszára.

4.3 A PIO üzemmódjának kiválasztása

A PIO A csatornája a következő négy üzemmódban működhet:

0. mód (kimeneti),

1. mód (bemeneti),

2. mód (kétirányú),

3. mód (vezérlő mód).

A B csatorna a 2. üzemmódot kivéve ugyanilyen üzemmódokkal rendelkezik.

Az üzemmód meghatározása a következő formátumú vezérlő utasítással történik:

Az üzemmódot a D7 és D6 bitek bináris kódja adja meg az alábbi táblázat szerint:

üzemmód 0 (kimeneti) 1 (bemeneti) 2 (kétirányú) 3 (vezérlő)

A D5 és D4-es biteket nem használják, és a D3-D0 bitek 1111 állapota jelzi, hogy üzemmód beírás történik.

A 0-ás üzemmód lehetővé teszi, hogy a CPU adatokat továbbítson a PIO kimeneti regisztereibe. A regiszterek tartalma megváltoztatható, ha a CPU új adatot küld ugyanarra a csatornára. A kimeneti regiszterek tartalma visszaolvasható a CPU-ba, ha a CPU beolvasó utasítást hajt végre.

0-ás üzemmódban a CPU felöl érkező adat a megfelelő csatorna READY handshake jelét logikai 1-be állítja, ami jelzi a periféria számára az új adat megjelenését. Ez a jel addig marad 1-es állapotban, amíg a periféria STROBE jele meg nem érkezik. A STROBE jel felfutó éle megszakítást generál (ha a megszakítás kérés engedélyezve volt), ami a READY jelet inaktív állapotba állítja. Ezt az egyszerű handshake adatátvitelt a legtöbb perifériánál alkalmazzák.

Az 1-es üzemmód kiválasztása bemeneti állapotba állítja a megfelelő csatornát. A "handshake" adatátvitel a CPU beolvasó utasításával indítható el. Ez aktivizálja a READY jelet, ami jelzi a perifériának, hogy adatot kell betölteni az üres bemeneti regiszterbe. A periféria ekkor a STROBE jellel betölti az adatot a csatorna bemeneti regiszterébe. A STROBE felfutó éle itt is megszakítást kér (ha engedélyezve volt) és megszünteti a READY jelet. A READY jel állapotától függetlenül is beírhatók adatok a bemeneti regiszterekbe, de ilyenkor vigyázni kell, nehogy felülírást következtében értékes adatok vesszenek el.

A 2-es üzemmód kétirányú adatátvitelt jelöl ki, amely felhasználja mind a négy handshake vonalat. Éppen ezért csak az A csatorna használható ebben az üzemmódban. Ilyenkor az A csatorna jelei vezérlik a kimenetet és a B csatornáé pedig a bemenetet. Így egyidejűleg lehet mindkét csatorna RDY jele aktív állapotban. A 0-ás és a 2. üzemmód kimeneti üzeménél csak annyi a különbség, hogy az A csatorna kimeneti regiszterét csak az A STB engedélyezi a kétirányú adatátvitelnek megfelelően.

A 3. üzemmód státusz és vezérlési célokat szolgál és így nem használja a handshake jeleket. Amikor a 3. üzemmódot állítjuk be a következő vezérlő utasítás meghatározza, hogy melyik csatorna adatbusza lesz kimenet és melyik bemenet. A vezérlő utasítás formátuma a következő:

Az 1-es bitek a megfelelő adatbusz vonalat bemenetnek állítják. Ennek megfelelően a 0-ás bitek kimenetnek állítják a megfelelő adatbusz vonalat.

A 3. üzemmódban a STROBE jel hatástalan és a READY jel folyamatosan 0-ban van. Ebben az üzemmódban a CPU kivihet és beolvashat adatokat a csatornákról, kivéve, ha az A csatorna 2-es, és a B csatorna 3-as üzemmádban van. Amikor a CPU beolvas valamelyik csatornáról az adat a kijelölt bemeneti és kimeneti bitek kompozíciója lesz.

4.4 A megszakítás vezérlő szó beállítása

A megszakítás vezérlő szó minden csatornánál a következő formátumú:

Ha a D7 bit = 1 a csatorna megszakítást engedélyező tárolója beíródik és a csatorna megszakítást tud kérni. Ha a D7 bit = 0, akkor a tároló törlődik és megszakítást nem lehet kérni. Ha megszakítás kérés történik mialatt D7 = 0, akkor ezt a PIO eltárolja és továbbítja a CPU-nak, amikor a megszakítás újra engedélyezve lesz (D7=1). A D4-D6 bitek főleg a 3-as üzemmódban használatosak, de a D4-es bit beírása minden üzemmódban törli a folyamatban lévő megszakítást. A D4-D6 bitek a megszakítás feltételeit határozzák meg a 3-as üzemmódban. A D6-os (AND/OR) bit határozza meg a logikai műveletet a csatorna I/O vonalainak figyelésénél. Ha D6 = 1, akkor logikai ÉS művelet, ha pedig D6 = 0, akkor logikai VAGY művelet lesz kijelölve. Például, ha ÉS művelet volt kijelölve az összes bitnek be kell állnia a meghatározott állapotba ahhoz, hogy megszakítás kérést generáljon a PIO, míg VAGY művelet kijelölésénél elég ha bármelyik meghatározott bit aktív állapotba megy.

A D5-ös bit határozza meg a csatornák adatbuszainak aktív állapotát. Ha D5 = 1 az adatvonalak logikai 1 szintje lesz aktív, ha pedig D5 = 0, akkor az adatvonalak logikai 0 szintjét veszi aktív állapotnak a megszakítást kérő logika.

Ha D4 = 1, akkor a következő vezérlő utasítás a PIO maszk regiszterét állítja be a következő formátum szerint:

Csak azok a csatorna vonalak lesznek érvényesek megszakítás generálásakor, amelyek maszk bitjei nullák.

A megszakítás engedélyező tároló a következő vezérlő utasítással beírható, vagy törölhető anélkül, hogy a megszakítás vezérlő szót módosítanánk:

| Megsz. eng. |

X |

X |

X |

0 |

0 |

1 |

1 |

Ha egy külső, aszinkron megszakítás érkezik mialatt a processzor letiltó utasítást küld a PI0-ba (03H), hiba keletkezhet.

Ha a processzorban a megszakítás kérés engedélyezve van, aszinkron megszakítás keletkezhet mialatt a CPU letiltó szót küld a PI0-nak. Ebben az esetben a PIO,INT jelet küld a CPU-nak, amit az elfogad, de a folyamatban lévő letiltó utasítás leállítja a PIO megszakítási egységeit. Ennek következtében a PIO nem küld megszakítási vektort a CPU-nak, ami így egy hibás megszakítási rutinba lép, ami program hibát okoz. A hibát úgy lehet elkerülni, hogy a PIO megszakítás kérésének letiltó utasítása előtt a DI utasítással letiltjuk a megszakítás engedélyezést a processzorban, majd a PIO vezérlő utasítás után újra engedélyezzük, az EI utasítással. Ez megakadályozza, hogy a letiltásban lévő PIO bármilyen hibás megszakítást kérhessen. Az ennek megfelelő programrészlet a következő:

...

LD A,03H

DI

OUT (PIO),A

EI

...

; CPU letiltása

; PIO letiltása

; CPU engedélyezése

5.1 Kimeneti üzemmód (0-ás üzemmód)

A 0-ás üzemmódhoz tartozó időzítést az 5.0-1a ábra mutatja.

5.0-1a: 0-ás üzemmód időzítése

Egy kimeneti ciklus mindig a CPU kimenő utasításának végrehajtásával kezdődik. A PIO által generált WR jel írja be az adatokat a CPU adatbuszáról a PIO megcímzett csatornájának kimeneti regiszterébe. Az órajel következő lefutó élénél ez a WR jel viszi logikai 1 szintre a READY jelet, ami jelzi a perifériának, hogy az adatátvitelre készen áll. A legtöbb rendszerben a READY jelet beíró impulzusnak használják a perifériában. A READY jel addig marad aktív állapotban, amíg a STROBE jel felfutó éle meg nem érkezik, ami jelzi, hogy a periféria az adatokat tárolta (lásd 5.0-la ábrát).

Ha a STROBE jel felfutott, másfél óraciklus múlva a READY jel lefut és beíródnak a csatornák kimeneti regiszterei. A READY jel visszatér 1 állapotba az órajel lefutó élére, miután az IORQ jel lefutott (lásd 5.0-1b ábra).

5.0-1b: 0-ás üzemmód időzítése

Ez az eljárás garantálja, hogy a READY inaktív állapotban marad, amíg a csatornákon az adat változik és akkor változik, amikor a kimeneti utasítás már végrehajtódott.

Ha a READY kimenetet rákötjük a STROBE bemenetre, egy óraciklus szélességének megfelelő szélességű impulzus állítható elő, amit az 5.0-1c ábra mutat.

5.0-1c ábra: a 0-ás üzemmód időzítése, ha a READY / STROBE vezetékek össze vannak kötve

A READY/STROBE jel pozitív éle nem állit elő megszakító jelet, mert ez az impulzus keskenyebb, mint az M1 jel, ami a PIO struktúrájának megfelelően nem generál megszakítást.

Ha a PIO nincs RESET állapotban (azaz vezérlő üzemmód lett kiválasztva), a kimeneti regiszter betölthető, mielőtt a 0-ás üzemmódot beprogramoznánk. Ez lehetővé teszi, hogy a kimenetek a felhasználásnak megfelelő aktív állapotba kerüljenek. Például, feltételezve, hogy logikai 1 szintű kimenetek szükségesek, a következő beállító rutint kell végrehajtani:

5.2 Bemeneti üzemmód (1-es üzemmód)

A bemeneti üzemmód időzítését az 5.0-2a/b-es ábra mutatja.

5.0-2a ábra

Ezt a ciklust a STROBE jellel kezdeményezi a periféria azután, hogy a CPU adatbeolvasást hajtott végre. A STROBE vonal alacsony szintje (0) betölti a csatorna bemeneti regiszterét és a felfutó éle pedig aktivizálja az (INT) megszakításkérő vonalat, ha a megszakítás kérés engedélyezve van és ez a legnagyobb prioritású egység. Az órajel következő lefutó éle törli a READY jelet megakadályozva, hogy újabb adat íródjon a bemeneti regiszterbe, mielőtt a CPU kiolvasást hajtana végre. Ekkor a CPU a megszakítási rutinjával beolvassa az adatot a megszakító eszközről. Ezután a CPU RD és az órajel lefutó éle felemeli a READY vonalat jelezve, hogy új adat tölthető a PI0-ba.

Miután a RESET állapot inaktív állapotba hozta a READY jelet, sok rendszernél egy üres bemeneti utasítás szükséges a READY jel aktivizálásához, ami megkezdi az adatátvitelt.

Ha a READY jel már aktivizálódott, másfél óraperiódusig 0 szinten marad az IORQ-jel felfutó éle után, mialatt a PIO kiolvasása történik (5.0-2b ábra).

5.0-2b ábra

Ha a felhasználó csak akkor ír be adatot, ha a READY 1-ben van ez megakadályozza, hogy beolvasáskor megváltozzanak a bemeneti regiszter adatai. Az előbbi leírásnak megfelelően a READY jel az IORQ jel felfutó éle után ismét 1-be megy.

5.3 Kétirányú üzemmód (2-es üzemmód)

Ez nagyjából megfelel a 0 és az 1 üzemmód kombinációjának, és felhasználja mind a négy handshake vonalat. Ennek megfelelően ez az üzemmód csak az A csatornán jelölhető ki.

Amikor az A csatorna ebben az üzemmódban van a B csatornának bit vezérlő üzemmódban kell lenni. Ugyanaz a megszakítási vektor lesz érvényes, mint a B csatornáé a 3. üzemmódban. Az ebből eredő probléma elkerülhető, ha a B csatorna lekérdezéses üzemben működik és a maszk regisztere letilt minden bitet. Továbbá a B csatorna nem fog megszakítást generálni, ha az A csatorna 2-es üzemmódban van. Az üzemmód időzítését az 5.0-3 ábra mutatja.

Ez majdnem ugyanaz, mint ami a 0. és 1. üzemmódnál lett leírva, azzal a kiegészítéssel, hogy a kimeneti adatátvitel vezérlését az A csatorna, a bemeneti adatátvitelt pedig a B csatorna "handshake" jelei vezérlik. A két üzemmád között az a különbség, hogy a 2-es üzemmódban csak akkor kerülhet adat a buszra, ha az A csatorna STROBE 0 szintű. Így a STROBE jel felfutó élével lehet beírni az adatot a perifériába, mivel ezután az adat stabil marad. A 2. üzemmód bemeneti része azonos az 1-es üzemmódéval. Megjegyzendő, hogy mindkét csatornánál engedélyezni kell a megszakítást, hogy a megszakításos üzemű kétirányú adatátvitel működjön.

A perifériának tilos adatot kapuznia a csatorna adatbuszára, mialatt az A STB jel aktív. A busz tilos használata elkerülhető, ha a periféria a B STB jelet használja a kapuzásra. Ezt a jelet a PIO akkor használja, amikor mintát vesz ebből az adatból. A PI0-t úgy tervezték, hogy nincs szüksége tartási időre, amikor az adatot beírják és így megengedhető, hogy a mintavételezés és a kapuzás egyszerre történjen. Másképpen, az adat letiltható a buszról közvetlen azután, hogy a STROBE jel felfutott. Megjegyzendő, hogyha az A csatorna kiolvasásakor az A STB jel logikai nulla szinten van, a CPU a kimeneti regiszter tartalmát fogja beolvasni a bemeneti regiszter helyett. Az A STB = 0 esetben a CPU nem tudja kiolvasni a bemeneti regiszter pontos tartalmát. Ha a CPU olvasó ciklusa közben az A STB jel le tud futni, meg kell akadályozni, hogy elérje a PIO A STB bemenetét, amíg a BRDY = 0 (a CPU akkor olvas, amikor BRDY=0 és az RD jel állítja vissza a BRDY-t 1-be).

5.4 Vezérlő üzemmód (3-as üzemmód)

A vezérlő üzemmód nem használja a "handshake"jeleket és a csatornák írása, vagy olvasása bármikor végrehajtható. Íráskor az adat a 0-ás üzemmódnak megfelelő időzítéssel tárolódik be a kimeneti regiszterbe. Az A csatorna 3-as üzemmódjában az A RDY jel 0-ba van kényszerítve. Ugyanez érvényes a B csatornára is, kivéve, ha az A csatorna 2-es üzemmódban van. Az utóbbi esetben a B RDY jel nem módosul.

Amikor a CPU adatot olvas be a PI0-ról az egyrészt annak a csatornának a kimeneti regiszter tartalma lesz, amelyiknek az adatvonalai kimenetként lettek kijelölve, másrészt annak a csatornának a bemeneti regiszter tartalma, amelyiknek az adatvonalai bemenetének lettek kijelölve. A bemeneti regiszter azt az adatot fogja tartalmazni, amelyik közvetlenül az RD jel lefutó éle előtt jelen volt. Lásd az 5.0-4a ábrát.

5.0-4a ábra: A vezérlő üzemmód időzítése

Megszakításkérés akkor jön létre, ha a csatornán a megszakítás engedélyezve van és a csatorna adatvonalain lévő adat megfelel a 8 bites vezérlő- és maszk regiszterek által meghatározott logikai feltételeknek. Másféle megszakítás addig nem lehetséges, amíg az engedélyező logikai feltételeket meghatározó státusz meg nem változik. Például, ha a 3-as üzemmódban a megszakítás kijelölt logikai feltétele "VAGY" kapcsolat, akkor ha a csatorna egy nem maszkolt adatvonala aktív állapotba megy, megszakítást fog eredményezni. Ha a csatorna egy második nem maszkolt adatvonala szintén aktív állapotba megy mialatt az előző is abban marad, nem lesz újabb megszakítás kérés addig, amíg a logikai hálózat kimenetén változás nem történik. Megjegyzendő, hogy annak a csatornának a bitjei amelyik kimenetként lett programozva hatással vannak a logikai hálózatra, he, nincs maszkolva.

Ha az M1 impulzus előtt, vagy alatt a logikai hálózat kimenete aktív állapotba kerül, az M1 jel felfutó éle után a PIO megszakítást kér a CPU-tól, feltételezve, hogy a logikai hálózat kimenete az M1 felfutása után is aktív marad. Az 5.0-4b ábrán egy 3. üzemmódban lejátszódó megszakításra láthatunk példát.

5.0-4b ábra: Megszakítási példa a 3. üzemmódban

A 3. üzemmódba állított csatornánál logikai VAGY kapcsolat és 1 szintű aktív állapotok lettek kijelölve. Az A0 és A1 vonalakon kívül minden adatvonal maszkolt és így egy kétbemenetű VAGY kapunak megfelelő logikai hálózatot kapunk. Az ábrán előszőr az A0 felfutására a PIO megszakítást kér a CPU-tól (INT jel lemegy), amire a CPU egy megszakítást elfogadó ciklussal (INTA) válaszol, hogy elfogadta a megszakítást. A PIO ekkor kiadja a csatornának megfelelő megszakítási vektorát a CPU adatbuszára és a CPU az ehhez tartozó megszakítási rutinra tér át. Az A0 ezután magától, vagy a megszaktó rutin hatására visszatér az eredeti állapotába (és így inaktiválja a logikai hálózat kimenetét). Az ábrán egy nyíl mutatja azt az időt, amikor a CPU kiadja a RETI (Return from Interrupt) utasítást, ami törli a PIO megszakítási logikáját.

Másodszor az A1 jel fut fel az ábrán, ami az előzőhöz hasonló megszakítást kér és kap. Az ábráról két fontos dolog olvasható ki:

A PIO megszakítás kérése után a CPU megszakítás elfogadó ciklussal válaszol (M1 és IORQ). Ebben az időben a PIO megszakítási logikája meghatározza a legmagasabb prioritású, megszakítást kérő csatornát (ez egyszerűen úgy történik, hogy a PIO megszakítást engedélyező bemenete 1-ben, míg az ugyanilyen kimenete 0-ban van). Ahhoz, hogy a megszakítási lánc stabil maradjon a PIO úgy lett kialakítva, hogy az M1 impulzus alatt a megszakítást kérő státusza ne válthasson. A legmagasabb prioritással rendelkező egység kiadja megszakítási vektorát az adatbuszra.

A megszakítás kérés időzítését a 6.0-1 ábra mutatja.

6.0-1 ábra: A megszakítás elfogadásának időzítése

Az M1 impulzus alatt új megszakítás kérés nem lehetséges és ez az idő elég arra, hogy a megszakítást engedélyező jel végigfusson a négy PIO egységen. Az első PIO, amelyiknek az IEI bemenete 1-ben és az IEO kimenete 0-ban van, az INTA alatt kiadja a megszakítási vektorát az adatbuszra.

Ha valamelyik PIO megszakítás kérését a CPU elfogadta, a PIO IEO kimenete 0-ban marad addig, amíg a CPU a RETI utasítást végre nem hajtja (az IEI bemenet végig 1-ben van). Ha a CPU a megszakítás kérést nem fogadja el a PIO egy M1 ciklusra 1-be állítja az IEO kimenetét, miután vette az ED utasítás kódját. Ez az eljárás biztosítja, hogy a RETI utasítást a megfelelő PIO fogja dekódolni (lásd a 6.0-2 ábrát).

6.0-2 ábra: A RETI ciklus időzítése

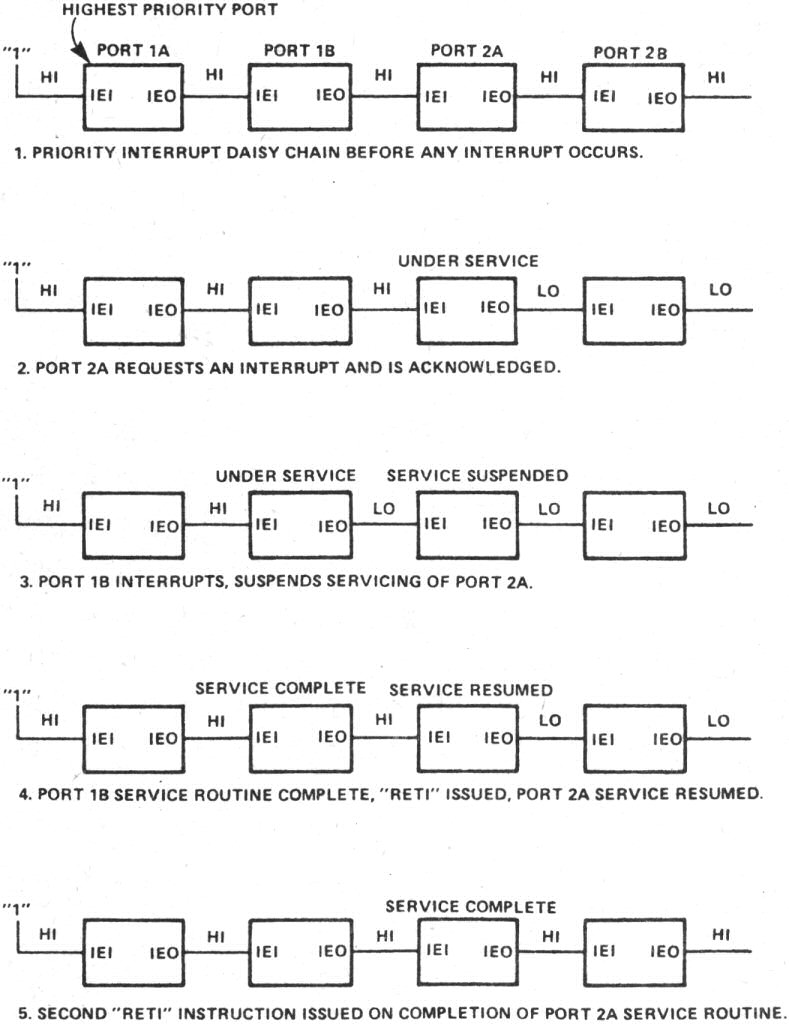

A 6.0-3-as ábra egy tipikus, láncolt megszakítási folyamatot mutat be, ahol négy csatorna van láncba kötve. A folyamatban először a 2A csatorna kér és kap megszakítást. Mialatt ez a kiszolgálás folyik a magasabb prioritású 1B csatorna kér és kap megszakítást. A magasabb prioritású csatorna kiszolgálásának befejezését a RETI utasítás jelzi a csatorna számára. Ezután a megszakított, alacsonyabb prioritású egység kiszolgálása folytatódik, majd ennek befejeztével a CPU folytatja az eredeti (megszakítások előtti) programját.

6.0-3 ábra: A láncolt megszakítás kiszolgálása

7.1 A megszakítási lánc kiterjesztése

Külső áramkör felhasználása nélkül max. 4 db PIO köthető megszakítási láncba. A korlátozás az M1 és az IORQ jelek közötti rövid idő miatt szükséges.

A PIO megszakítást kérő státusza az M1 alatt nem változhat, a legmagasabb prioritású egység fogja beadni a megszakítási vektorát.

Ha több mint négy PI0-t kell sorbakötni, akkor előrecsatoló hálózatot kell kiépíteni (lásd a 7.0-1 ábrát).

7.0-1 ábra: A prioritásos megszakítási lánc kiterjesztése

Ezzel a struktúrával és normál TTL áramkörök felhasználásával több, mint 30 PIO láncolható egymás után.

7.2 I/O Periféria

Ebben a példában a Z80-PIO egy kétirányú adatvonallal rendelkező perifériával van összekötve, amely a 7.0-2 ábrán látható.

7.0-2 ábra: Példa az I/O perifériára

A 2. (kétirányú) üzemmódot a következő utasítás választja ki:

Ezután a megszakítási vektor betöltése következik (lásd a CPU megszakításának leírását):

A megszakítást vezérlő logika beállítása után (enélkül M1 megszakítás elfogadó ciklust határoz meg), az M1 felfutó éle engedélyezi a megszakítást.

Ha maszk betöltő utasítás követi a megszakítás vezérlő utasítást, az M1 felfutó éle ezután engedélyezi a megszakítást. Ekkor a CPU és a PIO között megkezdődhet az adatátvitel. (Az adatátvitel időzítését az 5. fejezet tartalmazza.)

7.3 Periféria vezérlés

A 7.0-3 ábra a PIO egy tipikus vezérlő felhasználására mutat példát.

Az ára egy ipari folyamat megfigyelését mutatja be, ahol a folyamat működését ellenőrző paraméterek a Z80-PIO-n alapuló rendszerbe jutnak. A folyamat vezérlő és státusz szava a következő formátumú:

A PIO felhasználása a következő: először az alábbi formátumú utasítás 3. üzemmódba állítja az A csatornát.

A 3. üzemmód kiválasztása után következő vezérlő utasítás (amit a CPU küld) mindig az I/O-t kiválasztó utasítás. Ebben a példában a csatorna adatvonalainak A5, A3 és A0 bitjeit szeretnénk kijelölni bemenetnek, amit a következő vezérlő utasítás hajt végre:

Ezután a szükséges megszakítási vektor betöltése következik:

A következő utasítás a csatorna megszakítás vezérlését állítja be:

Ezt a maszk utasítás betöltése követi:

A5, A3 és A0 kiválasztása megfigyelésre

Így, ha egy érzékelő logikai 1 szintet ad az A5, A3 vagy az A0 vonalakra, akkor megszakítás kérés történik.

A maszk utasítás a bemenetek és kimenetek bármely kombinációját kiválaszthatja a megszakításhoz. Például, ha a fenti maszk utasítás a következő lenne:

akkor a 7. bit 1-be (speciális teszt) állítása is megszakítás.

Tételezzük fel, hogy a következő csatorna elnevezéseket használják:

E0H = A csatorna adat

E1H = B csatorna adat

E2H = A csatorna vezérlés

E3H = B csatorna vezérlés

Minden csatorna száma hexadecimális kódban van. Ez a kiosztás általános, mert így a címbusz A0 bitje használható, mint csatorna választó jel, az A1-el pedig a C/D bemenetet lehet vezérelni. A chip engedélyező bemenetet (CE) vagy közvetlenül a címbusz 7. bitje, vagy nagyobb rendszereknél a címbusz A7-A2 (111000) jelek dekódolásával kapott jel vezérelheti.

8.1 Megszakítási vektor betöltése

8.2 Üzemmód beállítás

| Üzemmód száma | M1 |

M0 | Üzemmód |

| 0 | 0 |

0 |

Kimenet |

| 1 | 0 |

1 |

Bemenet |

| 2 | 1 |

0 |

Kétirányú |

| 3 | 1 |

1 |

Bit vezérlő |

A 3. üzemmód kiválasztásánál a következő PIO-nak kiküldött szó az I/O regisztert tölti fel:

| I/O = 1 | a vonalat bemenetre állítja |

| I/O = 0 | a vonalat kimenetre állítja |

8.3 Megszakítás vezérlés beállítása

Ha a "maszk köv." (maszk következik) bit 1, akkor a következő vezérlő utasítás a maszk:

| MB = 0 | A bitet a megszakítás logika figyeli |

| MB = 1 | A bitet a megszakítás logika nem figyeli |

A csatornák megszakítás engedélyező tárolója a következő utasítással módisítható anélkül, hogy a megszakítás vezérlés többi része változna:

9.1 Maximális adatok

Üzemi hőmérséklet 0 - 70 C Tárolási hőmérséklet -65 - +150 C Feszültség -0,3 - +7V

(bármelyik lábon a földhöz képest)Disszipáció 0,6 W

9.2 DC jellemzők

9.3 Kapacitások

9.3-1 táblázat

9.4 Dinamikus adatok

9.4-1A táblázat: Az MK3881, MK3881-10, MK3881-20 Z80-PIO dinamikus adatai

9.4-1 ábra: Kimeneti terhelő áramkör

9.5 Időzitési diagram

| Típus | Megnevezés |

Tokozás | Max. óra | Működési hőmérséklet |

| MK3881N MK3881P MK3881J MK3881N-4 MK3881P-4 MK3881J-4 MK3881P-10 |

Z80-PIO Z80-PIO Z80-PIO Z80-PIO Z80-PIO Z80-PIO Z80-PIO |

műanyag kerámia kerámia műanyag keramikus kerámia keramikus |

2,5 MHz 2,5 MHz 2,5 MHz 4,0 MHz 4,0 MHz 4,0 MHz 4,0 MHz |

0 ... +70 C 0 ... +70 C 0 ... +70 C 0 ... +70 C 0 ... +70 C 0 ... +70 C -40 ... +85 C |

A Z80-CTC Áramkör

A Z80 számláló és időzítő (CTC) áramkör a Z80 bázisú rendszerek egy programozható perifériája, amely időzítő és számláló funkciókat lát el. A CPU által különféle üzemmódokba programozható áramkör a perifériák széles skálájával tud üzemelni. A legtöbb felhasználásnál semmi, vagy csak néhány kiegészítő áramkör szükséges. A Z80-CTC 28 lábú DIP tokozású áramkör, amely N csatornás, szilícium vezérlő elektródás, kiürítéses üzemmódú terhelő tranzisztoros technológiával készült. Az áramkör egy +5 V-os tápfeszültségről és egy egyfázisú órajellel működik.

Főbb tulajdonságai a következők:

12.1 A működés áttekintése

A Z80-CTC blokkvázlatát a 12.0-1 ábra mutatja, az áramkör a következő egységeket tartalmazza: Z80-CPU busz interface, belső vezérlő logika, négy számláló és időzítő áramkör és a megszakítás vezérlő logika.

12.0-1 ábra: A CTC blokkvázlata

A négy számláló és időzítő áramkör sorrend szerinti számokkal (0-3) vannak megkülönböztetve. A CTC önállóan is képes megszakítást kérni (automatikus megszakítási vektor beküldésével). A négy csatorna sorbaköthető egy prioritásos megszakítási láncba, ahol a 0. csatornának van a legnagyobb prioritása.

A CTC busz interface áramköre lehetővé teszi a közvetlen csatlakozást a CPU adatbuszára anélkül, hogy ehhez további külső áramköröket kellene felhasználni. Nagyobb rendszerek kiépítésénél természetesen további dekóderek és meghajtók felhasználása is szükséges lehet.

12.2 A csatornák felépítése

Az egyes (4 db) csatornák felépítését a 12.0-2 ábrán láthatjuk.

12.0-2 ábra: A csatornák blokkvázlata

A csatorna két regiszterből, két számlálóból és a vezérlő áramkörből áll. A CPU által kiolvasható, 8 bites lefelé számlálónak egy 8 bites előszámlálója is van.

12.2.1 A csatorna vezérlő egység

A 8 bites csatorna vezérlő regisztert a CPU tölti fel adattal és ezzel meghatározza a csatorna üzemmódját és paramétereit. A CTC a négy számláló és időzítő áramkörének megfelelően négy ilyen regisztert tartalmaz. Azt, hogy a négy regiszter közül melyik fog töltődni a CS0 és CS1-es bemenetek határozzák meg (erre a célra rendszerint a CPU címsínének A0-A1 bitjeit szokták használni). A CS0 és CS1 bináris kódja adja a hozzárendelt csatorna számát:

CS1 |

CS0 |

|

| 0. csatorna | 0 |

0 |

| 1. csatorna | 0 |

1 |

| 2. csatorna | 1 |

0 |

| 3. csatorna | 1 |

1 |

A csatorna vezérlő regiszterekbe irt utasítás 0. bitje mindig 1, míg a többi az alábbi formában különféle üzemmódokat és paramétereket határoz meg (részletesebben lásd a 4. és az 5. pontoknál):

12.2.2 Az előszámláló

Az egyes csatornákhoz egy-egy 8 bites előszámláló tartozik, melyek bemenetére a rendszer óra csatlakozik. Programozása a csatorna vezérlő regiszterrel történik és 256-os vagy 16-os osztásra alkalmas. A kimenete a lefelé számláló bemenetére jut, melynek kezdeti értéke a konstans regiszterből tölthető be. A konstans regiszter tartalma automatikusan átíródik a számlálóba, mikor az a nullához ér, de áttölthető a számláló külső óra/trigger bemenetének lefutó élével is. Minden alkalommal mikor a számláló eléri a nullát egy pozitív impulzust ad ki a nullátmenet = Zero Count/Timeout = ZC/TO.

12.2.3 Az idő állandó (konstans) regiszter

A konstans regiszter 8 bit széles és programozása a csatorna-vezérlő byte után következő 1-256 értékű számmal történik. A CTC alapállapotba állításakor és a számláló nulla átmeneténél a konstans regiszter tartalma automatikusan betöltődik a lefelé számláló regiszterbe. Ha a konstans regiszter új értéket kap mialatt időzítés vagy számlálás folyik, előbb befejezi a lefelé számlálást és csak azután tölti be a konstans regiszter új értékét a számlálóba. (Részletesen lásd az 5. pont "CTC programozása" címnél.)

12.2.4 A lefelé számláló

A lefelé számláló egy 8 bites, mindkét üzemmódban használható regiszter, amely alapállapotba állításkor és nullátmenetnél feltöltődik a konstans regiszter tartalmával. A számláló mindkét üzemmódban (időzítő és számláló) a bemenetére jutó minden aktív óraélre dekrementálódik.

Bemenete az előszámláló kimenetére csatlakozik. A CPU egy I/O olvasó ciklussal bármikor kiolvashatja a számláló tartalmát, ami a nulláig hátralévő számot tartalmazza. A CTC nullátmenetre történő, automatikus megszakításkérésre is programozható.

A 0,1 és 2. csatornánál, ha a számláló nullába ért, egy impulzust ad ki a csatornához tartozó ZC/TO (Zero Count /Timeout) kimeneten. A tokozás korlátozott kivezetésszáma miatt a 3. csatorna nem rendelkezik ezzel a kimenettel és így csak ott alkalmazható, ahol erre nincs szükség.

12.3 Megszakítás vezérlő logika

A megszakítás vezérlő logika biztosítja, hogy a láncolt, prioritásos megszakítás kérésénél és visszatérésénél a CTC a Z80 megszakítási protokoljának megfelelően működjék. Az egyes CTC-k prioritási szintjét a láncban elfoglalt fizikai helyük határozza meg. A CTC láncot az IEI és IEO jelek sorbakötésével alakítják ki és minél közelebb van egy CTC a CPU-hoz, annál magasabb a prioritási szintje. A CTC-n belül a 0. csatornának van a legmagasabb prioritási szintje és sorrendben tovább mindig kisebb (a 3. csatorna prioritása a legkisebb). A megszakítás kérés előnye, hogy a CTC azonnal a kiszolgáló rutinra vezérli a CPU-t. A Z80 megszakítási sémájának megfelelően egy alacsonyabb prioritási szintű egység nem szakíthatja félbe a magasabb prioritási szintű egység megszakítási rutinját, hanem csak annak befejeztével kap kiszolgálást.

A CTC úgy programozható, hogy automatikusan megszakítást kérjen, amikor a számláló eléri a nullát. (Ez a működés feltételezi azt, hogy CPU 2. üzemmódú megszakításra lett programozva.) Megszakítás kéréskor a CPU mindig kiad egy megszakítás elfogadó jelet, mialatt a CTC-k megszakítási logikái meghatározzák, hogy melyik egység melyik csatornája kért megszakítást. Ekkor, amelyik CTC megszakítást kért és az IEI bemenete engedélyezve van (ez jelzi, hogy ő a legnagyobb prioritású egység) kiadja a 8 bites megszakítási vektorát a CPU adatbuszára. Ennek a vektornak az öt legnagyobb helyiértékű bitjét a CTC alapállapotba állításánál kell beprogramozni. A következő két bit meghatározza, hogy a CTC-n belül melyik csatorna kérte a megszakítást. Az utolsó, legkisebb helyiértékű bit mindig nulla (lásd az alábbi ábrát).

Ez a megszakítási vektor egy pointer, amely a CPU memóriájában kijelöl egy helyet, ahol táblázatosan találhatók a megszakítási rutinok kezdőcímei. A vektor adja a memória címének alsó byte-ját, míg a CPU I regisztere adja a 16 bites cím felső byte-ját. A kijelölt cím tartalmazza a megszakítási rutin címének alsó byte-ját és a következő cím pedig a felső byte-ot. Így a 2. megszakítási üzemmódban a CTC 8 bites vektora egy indirekt címzésű megszakítási rutint tud elindítani.

A Z80 16 bites megszakítási pointerének kialakítása:

| I regiszter tartalma | 7 bit a perifériától (vektor) | 0 |

A Z80 rendszer előírásai szerint a címek alsó byte-jai mindig páros címen vannak és a felső byte-jaik pedig a következő páratlan címen találhatók. Ez az oka annak, hogy a megszakítási vektor utolsó bitje mindig nulla.

A RETI CPU utasítás jelzi a megszakítási rutin végét és alapállapotba állítja a megszakítási lánc IEO vonalát. A CTC figyeli az adatbuszt és dekódólja a RETI utasítást. Ebből a CTC tudja mikor van vége a megszakítási rutinnak anélkül, hogy ezt számára külön jelezni kellene.

A CTC lábkiosztását a 13.0-1 ábra mutatja.

13.0-1 ábra: A Z80-CTC lábkiosztása

| D7-D0 | CPU adatbusza (kétirányú, háromállapotú). Ezen a buszon folyik minden adat és vezérlés kommunikáció a CPU és a CTC között (D0 a legkisebb helyiértékű bit). |

|||||||||||||||

| CS1-CS0 | CS1-CS0 Csatorna választó bemenetek A bemenetekre adott bináris azám, négy különböző csatornát tud kiválasztani:

|

|||||||||||||||

| CE | Chip engedélyező bemenet (0 szinttel engedélyez). A 0 szint a bemeneten engedélyezi, hogy a CTC utasításokat és adatokat fogadjon el a CPU-tól, amikor az I/O írást hajt végre és kiolvasható a számláló tartalma, amikor a CPU I/O olvasást hajt végre. Általában a CPU címsínének alsó byte-jából szokták dekódólni úgy, hogy az utolsó két bitet meghagyják a CS0-CS1 számára. |

|||||||||||||||

Órajel |

Rendszer óra bemenet. Egyfázisú órajel, amely a CTC belső műveleteit szinkronizálja. | |||||||||||||||

| M1 | Az egyes gépi ciklus jele a CPU-tól (bemenet, a 0 szint aktív). Ha M1 és RD jelek aktívak, akkor a CPU utasítást olvas ki a memóriából. Ha M1-el együtt IORQ is aktív, akkor a CPU megszakítást fogad el és a CTC kiadja az adatbuszra a megszakítási vektorát, ha 0 a legnagyobb prioritású megszakító egység a láncban. |

|||||||||||||||

| IORQ | I/O kérés a CPU-tól (bemenet, a 0 szint aktív). A CE és RD jelekkel együtt vezérli az adatátvitelt a CPU és a CTC között. Íráskor a CE és IORQ aktív és ID nem. A CTC nem kap külön író jelet, hanem azt az RD jel invertálásával állítja elő. Olvasáskor a CE, IORQ és RD jelek aktívak és a CTC a számláló tartalmát adja ki a CPU adatbuszára. Ha az IORQ az M1-el együtt aktív a CPU megszakítást fogad el és a legnagyobb prioritású egység adja ki megszakítási vektorát. |

|||||||||||||||

| RD | Olvasó ciklust jelző vonal a CPU-tól, bemenet (a 0 szint aktív). Az RD jel, az IORQ és CE jelekkel együtt az adatátvitelt vezérel a CPU és a CTC között. Íráskor az IORQ és CE aktív, míg az RD nem. A CTC nem kap külön írásjelet, hanem azt az RD invertálásával állítja elő. Olvasáskor mindhárom jel (IORQ, CE, RD) aktív és a CTC a számláló regiszter tartalmát adja ki az adatbuszra. |

|||||||||||||||

| IEI | Megszakítás engedélyező bemenet (1 szint aktív). A megszakítási lánc kialakítására szolgál és logikai 1 szint ezen a bemeneten jelzi, hogy ez az egység a legmagasabb prioritású a láncban. |

|||||||||||||||

| IEO | Megszakítás engedélyező kimenet (1 szint aktív). Az IEI kivezetéssel együtt a megszakítási lánc kialakítására szolgál. Az IEO akkor van 1 szinten, ha az IEI 1 szinten van és a CPU nincs megszakítási rutinban. Ez a jel akadályozza meg az alacsonyabb prioritású egységek megszakítás kérését. |

|||||||||||||||

| INT | Megszakítás kérés kimenet (nyitott kollektoros, a 0 szint aktív). Megszakítás kéréskor a CTC ezt a vonalat nullába teszi. | |||||||||||||||

| RESET | Törlő bemenet (a 0 szint aktív) |

|||||||||||||||

| CLK / TRG3-CLK / TRGO |

Külső óra és trigger jel bemenet (programozható aktív él). Minden csatornához tartozik egy-egy ilyen bemenet. Számláló üzemmódban a bemenetre adott aktív él dekrementálja a számlálót. Időzítő üzemmódban a bemenetre adott aktív él indítja az időzítést. Az aktív él programozható, ami lehet fel vagy lefutó él. |

|||||||||||||||

| ZC / TO2-ZC / T00 |

Nullátmenet és időzítés kimenet (az 1 szint aktív). Az első három csatornának ezen a kimenetén 1 szint jelenik meg, amikor a számláló eléri a nullát (mindkét üzemmódban). |

A tápfeszültség bekapcsolásakor a CTC meghatározatlan állapotba kerül. A RESET bemenettel a CTC alapállapotba állítható. A csatornák üzembevétele előtt a csatorna megfelelő regisztereibe egy csatorna-vezérlő és egy konstans regiszter betöltő utasítást kell beírni. Ha a megszakítás engedélyezett, akkor a megszakítási vektort is be kell írni a megszakítási logika regiszterébe. (Részletesebben lásd az 15. pontban a "CTC programozása" címnél.) Amint a CPU ezeket az adatokat betöltötte az összes aktív csatorna azonnal megkezdi a számlálást vagy az időzítést,a programozástól függően.

14.1 A CTC számláló üzemmódja

Ebben az üzemmódban a CTC a CLK/TRG bemenetre adott impulzusok éleit számolja. Az üzemmód beállítása a csatorna vezérlő regiszter 6. bitjének 1-be programozásával történik. A számláló a CLK/TRG bemenetre adott aktív élre és a 0 rendszer órához szinkronizálva dekrementálódik. A számlálás megkezdése előtt a számláló felveszi a konstans regiszter értékét.

A bemeneti vezérlő él és az órajel felfutó éle között nincs előkészítési idő definiálva, de a számláló mindig csak a következő órajellel dekrementálódik. (Lásd a ts/CK/ paramétert a 18. pontban.) A külső óra bemenet aktív éle a csatorna vezérlő regiszter 4. bitjével programozható.

A 0, 1 és 2 csatornánál, ha a számláló elérte a nullát a csatorna ZC/TO kimenete aktív állapotba (1) kerül. (A kivezetés korlátozás miatt a 3. csatorna nem rendelkezik ezzel a kimenettel és így csak ott használható, ahol erre nincs szükség.) Ha a számláló tartalma 0 lett és a csatorna-vezérlő regiszter 7. bitjének 1-be programozásával a megszakítás kérés engedélyezve volt, megszakítás kérés is lesz. (Részletesebben lásd a 7. pontnál a "CTC megszakítás"-t.)

A fenti műveletek közben a lefelé számláló automatikusan felveszi a konstans regiszter tartalmát anélkül, hogy a számlálást megszakítaná. Ha a lefelé számolás közben a konstans regisztert újra töltik, akkor az új értéket a számláló csak a számlálás befejezése után veszi fel.

14.1-0 ábra: Csatorna-számláló üzemmód

14.2 CTC időzítő üzemmód

Az üzemmódban a CTC a rendszer óra idejének többszörösével megegyező idejű időzítő impulzust tud előállítani. Az időzítő üzemmód a csatorna-vezérlő regiszter 6. bitjének törlésével programozható. A rendszer óra két sorba kötött számlálóra (előszámláló és lefelé számláló) kerül és így a csatorna időintervallum előállítására alkalmas. A csatorna-vezérlő regiszter 5. bitjének megfelelően az előszámláló 16-al vagy 256-al osztja a rendszer órajelet. Az előszámláló kimenete a lefelé számláló bemenetére csatlakozik, amely 1-256 kezdeti értékre tölthető fel. Ha a lefelé számláló eléri a nullát automatikusan feltöltődik a kezdeti értékre (konstans regiszter tartalma). A számláló nullátmeneténél a csatorna ZC/TO kimenetén egy impulzus jelenik meg és két ilyen impulzus közötti időt az alábbi összefüggés adja:

tc * P * TC

ahol:

tc a rendszer órajelének periódus ideje P az előszámláló osztása (16 vagy 256) TC a beprogramozott konstans

Az időzítés indítását a csatorna vezérlő 3. bitje határozza meg. Ha a 3. bit törölve van (0) az időzítés a konstans regiszter betöltését követő CPU ciklussal kezdődik. Ha 3. bit egyben van, akkor a csatorna időzítés a konstans regiszter betöltése után az időzítő trigger (CLK/TRG) jelet követő második órajel felfutó élénél kezdődik. Ha nincs konstans regiszter betöltés, akkor az időzítés a csatorna vezérlő betöltést követő trigger jel után a második órajel felfutó élénél kezdődik. A csatorna vezérlő regiszter 4. bitje határozza meg, hogy az időzít / triggerelő bemeneten a fel, vagy a lefutó él legyen aktív.

A trigger jel aktív éle és az órajel között nincs előkészítési idő definiálva. Ha a trigger jel túl közel kerül az órajel felfutó éléhez, akkor a lefelé számláló csak a következő órajel felfutó élénél kezdi meg a számlálást (lásd a ts/TR) paramétert a 18.3. pont AC karakterisztikáinál).

Ha a csatorna vezérlő regiszter 7. bitje 1-be volt programozva a lefelé számláló nullátmeneténél a kimeneti (ZC/TO) impulzus megjelenésével együtt automatikus megszakítás kérés is lesz (részletesebben lásd a 7. pontban a "CTC megszakítás kiszolgálás"-t).

Mielőtt a CTC megkezdené az időzítő, vagy a számláló üzemmódját a CPU-nak be kell töltenie a csatorna vezérlő és a konstans regisztereket. Ha bármelyik csatorna vezérlő regiszter 7. bitje engedélyezi az automatikus megszakítást, egy megszakítási vektort is be kell írni a CTC megfelelő regiszterébe. A megszakítás vezérlő logika felépítésének megfelelően ez a vektor szolgál mind a négy csatorna megszakítás kéréséhez.

15.1-0 ábra: A csatorna blokkvázlata

15.1. Csatorna vezérlő regiszter betöltése

A csatorna vezérlő regiszter betöltését a CPU egy normál I/O írással hajtja végre. Azt, hogy a beírás melyik csatornára érvényes, a CS0 és CS1 bemenetek bináris értéke határozza meg. A legtöbb rendszernél ez a két bemenet a CPU címsínének A0 és A1 vonalára van kötve, ami fix címet biztosít a CTC egyes csatornáinak. Ha a CTC-be irt adat 0. bitje 1, akkor a CTC ezt utasításnak értékeli és betölti a csatorna vezérlő regiszterbe. Az utasítás további hét bitje a következő kiosztással különböző vezérléseket állit be:

A csatorna vezérlő regiszter kiosztása:

7. bit = 1

Ebben az esetben a csatorna megszakítást kér minden esetben, amikor a számláló eléri a nullát. Ha ez a bit bármelyik csatornánál 1-be lett írva a CTC működésének megkezdése előtt, a megszakítási vektort is be kell tölteni.

7. bit = 0

A csatorna megszakítás kérése tiltva van. Minden függőben lévő megszakítási folyamatot letilt.

6. bit = 1

Számláló üzemmód kijelölése. A lefelé számláló minden külső óra élre (CLK/TRG) dekrementálódik. Az előszámláló nem üzemel.

6. bit = 0

Időzítő üzemmód beállítása. Az előszámláló leosztja a rendszer órát és a kimenete a lefelé számláló bemenetére csatlakozik. A lefelé számláló kimenete adja ZC/TO kimeneten az időzítést, melynek periódus ideje a következő összefüggéssel számolható:

tc * P * TC

ahol:

tc - a rendszer óra periódus ideje

P - az előszámláló leosztása (16 vagy 256)

TC - a konstans regiszter tartalma

5. bit = 1

Az előszámláló leosztása = 256

5. bit = 0

Az előszámláló leosztása = 16 (az előszámláló csak időzítő üzemmódban működik).

4. bit = 1

Időzítő üzemmódban az időzítés a külső trigger jel felfutó élére indul.

Számláló üzemmódban a külső óra pozitív (felfutó) élére dekrementálódik a számláló.

4. bit = 0

Időzítő üzemmódban az időzítés a külső trigger jel lefutó élére indul.

Számláló üzemmódban a külső óra lefutó élére dekrementálódik a számláló.

3. bit = 1

Csak időzítő üzemben érvényes. Az időzítés külső triggerrel indítható és a konstans regisztert betöltő utasítás második gépi T2 ciklusának felfutó élénél kezdődik. Az előszámláló dekrementálása két óraciklussal később kezdődik (ha az órajel és a vezérlőjel közötti idő kicsi, akkor három ciklussal később kezdődik).

3. bit = 0

Csak időzítő üzemmódban érvényes. Az időzítés a konstans regiszter betöltő utasítás T2 gépi ciklusának felfutó élénél kezdődik.

2. bit = 1

A következő adat a konstans regiszterbe kerül. Ha a betöltésnél a számláló már működik az új értéket csak a nullátmenet után veszi fel.

2. bit = 0

Konstans regiszter betöltő adat nem jön, mert a csatorna már üzembe lett helyezve és a konstans regisztert már betöltötték, a vezérlő utasítás valamilyen más céllal érkezett. A konstans regiszter betöltése nélkül a csatorna nem működik megfelelően és csak a 2. bit vezérlése alatt lehet feltölteni.

1. bit = 1

Törlés programból; megáll a számlálás és az időzítés, de a csatorna vezérlő egyetlen bitje sem változik meg. Ha a 2. és 1. bit is 1-ben van a csatorna a konstans regiszter betöltése után folytatja a működését.

15.2. A CTC megszakítás kérésének letiltása

Ha egy aszinkron megszakítás kérés már elindult, amikor a CPU letiltja a CTC megszakítás kérését, hiba keletkezhet. Ez akkor lehetséges, ha előzőleg a megszakítás engedélyezve volt. A CTC ilyenkor INT jelet ad a CPU-nak, amit az elfogad, de közben a CTC megkapja a megszakítás letiltást, ami törli a teljes megszakítási logikát. Az eredmény az lesz, hogy a CTC nem küld megszakítási vektort a CPU-nak, mert már tiltva van, és a CPU egy hibás címre megy, ami program hibát okoz. A hibát úgy lehet elkerülni, hogy a CTC letiltása előtt egy DI utasítással letiltjuk a CPU megszakításának engedélyezését és a CTC letiltása után egy EI utasítással újra engedélyezzük. A következő programrészlet egy ilyen szekvenciát mutat be:

LD A,01H

DI

OUT (CTC),A

EI

; a CPU letiltása

; a CTC megszakításának letiltása

; a CPU megszakítás engedélyezése

15.3. A konstans (időalap) regiszter betöltése

Akár időzítő, akár számláló üzemmódban van a CTC, addig nem kezdheti meg a működését, amíg a CPU a konstans regiszter értékét be nem írta. A konstans regiszter adata a csatorna vezérlő betöltését követő I/O ciklusban érkezik a CPU-tól, ha a csatorna vezérlő utasítás 2. bitje 1-ben volt. A regiszterbe 1-256 közötti egész számok tölthetők. Ha a betöltés alatt a számláló, már számol, akkor az új érték csak a nullátmenet után íródik be a számlálóba.

A konstans regiszter adata:

15.4. A megszakítási vektor betöltése

A CTC megszakítási rendszere a Z80-CPU 2. üzemmódú megszakításával működik. Ennek az üzemmódnak megfelelően a CTC megszakítás kérésénél a CPU egy 16 bites pointert generál, amely egy táblázatból (a memóriában) meghatározza a megfelelő megszakítási rutin kezdőcímét. A pointer felső 8 bitjét a CPU I regiszterének tartalma adja, az első 8 bites pedig a CTC által megadott vektor, amely már tartalmazza azt is, hogy melyik csatorna kérte a megszakítást. (Részletesebben lásd a "CTC megszakitás kiszolgálása"-t a 17. pontban.)

A 2. üzemmódú megszakítási cím meghatározása:

A programozás kezdetén a megszakítási vektor felső öt bitjét kell beírni a CTC-be. Ezt úgy kell csinálni, mintha csatorna vezérlő utasítást küldenénk a CTC 0. csatornájára, de az utasítás 0. bitjének 0-ban kell lennie. (Ellenkező esetben csatorna vezérlő utasítás lesz.) Beíráskor az 1. és 2. bit érvénytelen, mert amikor a CTC kiadja a CPU-nak a megszakítási vektort, erre a két bitre írja be a megszakítást kérő csatorna címét.

A kiadott megszakítási vektor felépítése:

Ebben a fejezetben a CTC következő folyamatainak időzítését mutatjuk be: adatbeírás a CTC-be, adatkiolvasás a CTC-ből, számlálás és időzítés. A megszakítás időzítését a 7., a dinamikus adatokat pedig a 8.4. pontban találhatjuk meg.

6.1. CTC írás ciklus

A CTC írásának időzítését a 16.1-0 ábra mutatja. Ez érvényes a csatorna vezérlő, a konstans és a megszakítási vektor regiszterek betöltésénél.

16.0-1 ábra: A CTC írásciklusa

Az ábrán látható, hogy a CPU az írást a T1 alatti RD jel 1 értékével készíti elő. Lévén, hogy a CTC-nek nincs külön író bemenete, azt az RD jelből maga állítja elő. A T2 óraciklus alatt a CPU az íróciklust azzal kezdi, hogy 0 szintet ad a CTC CE és IORQ bemeneteire. (Az M1-nek hamisnak kell lennie, hogy a ciklust meg lehessen különböztetni a megszakítás elfogadó ciklustól.) Ugyanebben az időben jelennek meg a CS0 és CS1 jelek, melyek meghatározzák, hogy melyik csatornába töltődjön a CPU adatbuszán lévő adat. Ezzel minden rendelkezésre áll, hogy a CTC a megfelelő regiszterébe betöltse az adatot, ami a T3 felfutó élével szinkronizálva meg is történik. További Tw várakozási (Wait) állapotok beiktatása nem szükséges.

16.2. CTC olvasó ciklus

A CTC olvasó ciklusának időzítését a 16.2-0 ábra mutatja.

16.2-0 ábra: CTC olvasó ciklusa

Ez a szekvencia zajlik le mindig, amikor a CPU kiolvassa a számláló tartalmát. A T2 ciklus alatt a CPU az RD, IORQ és CE jelek aktivizálásával (0) készíti elő az olvasást. Ugyanebben az időben jelennek meg a CS0-CS1 jelek, amelyek meghatározzák, hogy melyik csatorna számlálóját olvassa ki a CPU. (Az Ml jelnek hamisnak kell lennie ilyenkor, hogy a ciklust meg lehessen különböztetni a megszakítás elfogadó ciklustól.) A kijelölt számláló regiszter tartalma a T3 felfutó élénél lesz érvényes az adatbuszon. További Tw várakozási ciklus beiktatása nincs engedélyezve.

16.3 CTC számlálás és időzítés

A CTC időzítésének és számlálásának időzítését a 16.3-0 ábra mutatja.

16.3-0 ábra: CTC időzítő és számláló üzeme

Számláló üzemmódban a CLK/TRG bemenetre jutó felfutó él (a példában ez az él lett programozva) az órajellel szinkronizálva dekrementálja a számlálót.

A CLK/TRG impulzus minimális szélessége nem lehet kisebb, mint a rendszer óra periódus idejének kétszerese. Bár nincs beállási idő (set-up time) definiálva a CLK/TRG és a rendszer óra között, ha CLK/TRG jel túl közel megy az órajelhez a számláló dekrementálása egy ciklust késik. Ahogy a számláló 1-ből 0-ba lép a ZC/T0 kimenet 1-be megy.

Időzítő üzemmódban a CLK/TRG impulzus aktív élét követő második órajel felfutó élétől kezdődik az időzítés. Ugyanúgy, mint a számláló üzemmódban a CLK/TRG jelnek minimális szélessége és ismétlődési ideje van. Az időzítés az órajellel szinkron indul és minimális beállási idő szükséges a CLK/TRG és az azt követő órajel felfutó éle között. Ha a két jel között kevesebb idő van, akkor az időzítés egy ciklussal késik.

17. CTC megszakítás kiszolgálás

Mindegyik CTC csatorna programozható úgy, hogy megszakítást kérjen, amikor a lefelé számlálójának tartalma eléri a nullát. A megszakítás kérés célja - mint minden más perifériánál - az, hogy a CPU-t egy meghatározott un. megszakítási rutinra kényszerítse. Ehhez a megszakításhoz a CPU-t 2. üzemmódú megszakításra kell programozni. Ennek az üzemmódnak megfelelően, amikor a CTC megszakítást kér és kap, a CPU egy 16 bites pointert állit elő (a megszakítási vektor felhasználásával), amely egy megszakítási táblázatból (a memóriában) kijelöli a megszakítási rutin kezdőcímét.

A pointer alsó 8 bitjét a CTC megszakítási vektora adja (ez már tartalmazza a megszakítást kérő csatorna azonosítóját is), a felső 8 bitet pedig a CPU I regisztere tárolja.

A Z80-nak megfelelő megszakítási és visszatérési folyamat lebonyolítását a CTC megszakítási logikája biztosítja. Az egyes CTC-k prioritási szintjét a láncban elfoglalt fizikai helyük határozza meg. A prioritásos megszakítási láncot a CTC IEI és IEO kivezetéseinek sorbakötésével lehet kialakítani. A láncban a CPU-hoz közelebb lévő CTC-nek van nagyobb prioritása. A CTC-n belül a 0. csatornának van a legmagasabb prioritása és sorban tovább egyre kisebb. A kisebb prioritású egység nem tudja megszakítani a magasabb prioritású egység kiszolgáló rutinját, mert az az IEO kimenetének 0-ba állításával letiltja az összes utána következő egység megszakítás kérését. A nagyobb prioritási szintű egység természetesen megszakíthatja a kisebb prioritású egység kiszolgáló rutinját.

17.1. Megszakítást elfogadó ciklus

A megszakítás elfogadó ciklust a 17.1-0 ábra mutatja.

17.1-0 ábra: Megszakítás elfogadó ciklus

Amikor a CTC megszakítást kér és kap, a CPU egy megszakítást elfogadó ciklussal válaszol (M1 és IORQ aktív). A megszakítási lánc stabilizálódása érdekében az M1 alatt tiltva van a csatornák megszakítási állapotának változása. Az M1 két óraciklussal előbb aktív mint az IORQ és az RD jel, hogy a ciklust meg lehessen különböztetni a memória hozzáférés ciklusától. Ezalatt az idő alatt a CTC-k megszakítási logikái azonosítják a legmagasabb prioritású megszakító egységet és az az IORQ jellel kiadja a megszakítási vektorát a CPU adatbuszára. Két beépített várakozási ciklus (wait) biztosítja, hogy a megszakítási lánc stabilizálódjon. További várakozási ciklusok is beiktathatók.

17.2. Visszatérés a megszakításból

A RETI utasítás időzítését a 17.2-0 ábra mutatja.

17.2-0 ábra: Megszakítás visszatérési ciklus

Ez az utasítás biztosítja a láncolt megszakítási rendszer megfelelő működését. A CTC-k dekódolják a két byte-os RETI utasítást és továbbítják a kiszolgálás alatt álló csatornának. A láncba kötött, több különféle típusú Z80 perifériák közül az áll kiszolgálás alatt, amelyiknek az IEI jele engedélyezett és az IEO jele nem. Ha a következő utasítás kód 4DH, a kiszolgálás alatt álló periféria megszakítási logikája alapállapotba áll és az IEO jele aktív lesz. Lehetőség van további várakozó ciklusok beiktatására.

17.3. Láncolt megszakítás kiszolgálás

A 17.3-0 ábra egy tipikus láncolt CTC megszakítási folyamatot mutat, ahol először a 2. csatorna kér és kap megszakítást. A megszakítás kiszolgálás folyamán a magasabb prioritású 1. csatorna is kér és kap megszakítást. Az 1. csatorna kiszolgálása után kiadja és végrehajtja a RETI utasítást a CPU és ezután folytatódik a félbeszakított 2. csatorna kiszolgáló rutinja.

17.3-0 ábra: Példa egy megszakítási lánc kiszolgálására

17.4. A CTC felhasználása megszakítás vezérlőként

A Z80 áramkörök mindegyike tartalmaz prioritásos megszakítási logikát, de elképzelhető, hogy olyan egységet kell a Z80 alapú rendszernek kiszolgálnia, amelyik ezzel nem rendelkezik. A CTC (MK3882) áramkörrel ez megoldható és a különféle típusú megszakítás kérését biztosító áramkörből 256 kapcsolható párhuzamosan.

Minden MK3882-es áramkörnek négy csatornája van és a számláló bemeneteken keresztül egy, vagy több (256-ig) impulzussal megszakítás kérhető. Az aktív él programozható (fel vagy lefutó élre). Minden csatornának külön megszakítási vektora van, amely jól felhasználható a Z80 2. üzemmódú megszakításánál. Megszakításkor a CPU I regiszterének tartalmából és a megszakítási vektorból nyerhető a megszakítási rutin címe. A prioritásos megszakítási folyamat teljes lebonyolítását a CTC végzi. Ha több mint egy CTC-t használnak, a prioritási lánc a CTC IEI és IEO kivezetéseinek sorbakapcsolásával alakítható ki. Minden csatorna megszakítás kérése külön-külön maszkolható.

Amikor az MK3882-t egy általános célú megszakítás vezérlőnek használjuk a megfelelő csatornát számláló üzembe állítva a konstans regiszterbe 1-t írunk. Beprogramozva a vezérlő jel aktív élét és a megszakítási vektort, az egység készen áll, hogy egy impulzus hatására megszakítást kérjen a CPU-tól.

Megszakítás kéréskor (a CPU 2. üzemmódú megszakítása) a CPU megkapja a perifériához tartozó megszakítási vektort, és rátér a megfelelő kiszolgáló rutinra. A megszakítás után és a RETI utasítás között a csatorna nem veszi figyelembe a bemeneti impulzusokat, de ugyanannak a CTC-nek egy másik csatornája félbeszakíthatja az előbbi megszakítási rutinját, ha magasabb a prioritási szintje.

Maximális adatok:

| Tárolási hőmérséklet | -65 - +150 C |

| Bemeneti feszültség | -0,3 - +7V |

| Disszipáció | 0,8 W |

8.1. DC adatok

8.2. Kapacitások

8.3. AC adatok (MK3882, MK3882-10), Z80-CTC

8.4. AC időzítés

8.5. AC adatok MK 3882-4, Z80A-CTC

Forrás: Zilog - Mostek (1981 febr.)

Vissza a Spectrum könyvekhez

Vissza az Enterprise könyvekhez